实话实说,现在的芯片工艺纳米很忽悠人,要看晶体管密度

2022年,三星、台积电宣称自己进入了3nm。

不过真正3nm芯片大规模量产,还是在2023年,苹果的A17Pro应该是首款,至于三星的3nm芯片,目前市场上并没有看到。

按照公布的信息来看,台积电、三星将在2025年实现2nm,而intel则表示自己会在2024年也就是今年实现2nm。

当然,3nm,2nm或者5nm也好,大家也不必太认真。

因为最重要的是,在14nm之后,各大晶圆厂关于芯片工艺到底是XXnm,已经是一团糟了,3nm未必就一定是3nm,2nm也未必就是2nm。

因为从14nm时,进入了FinFET晶体管时代,这种晶体管是立体的,不再像以前工艺节点和栅极长度、线宽一样是有关联的。

这时候的XX纳米,其实是一种等效工艺,因为不一定要缩小线宽,也能够实现性能的提升等。

所以从14nm开始,很多人认为所谓的多少纳米,其实已经是一种营销游戏了,这样说也没太多问题,但其实从14nm之后,关于芯片工艺,还有是一个评价标准的,那就是晶体管密度。

因为芯片是由晶体管运算来决定的,晶体管越多,性能肯定越强,同样单位面积下,晶体管越多,肯定工艺就越高,这是最简单的道理。

所以严格的来讲,当进入14nm之后,我们单独的说某一家晶圆厂进入了5nm、3nm并没有太多意义,实话实说,现在的芯片工艺纳米很忽悠人,要看晶体管密度而是要结合对方工艺的晶体管密度来看,那么谁在搞数字游戏,谁在认真造芯片,就一目了然了。

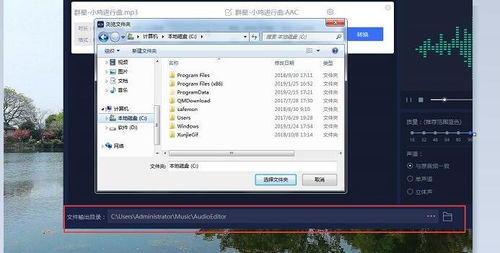

上图就是intel、台积电、三星在14nm到2nm时,典型工艺节点时,其晶体管密度,单位是百万/平方毫米。

可以看到在14nm时,intel是最牛的,达到了0.375亿颗每平方毫米,三星是0.329亿颗,而台积电当时是16nm只有0.29亿颗,台积电最落后,所以台积电只也称之为16nm。直到12nm时才追上来,达到0.36亿颗。这也是为何苹果的A7芯片,三星和台积电两家代工厂的原因,因为确实三星当时很强。

接下来是10nm时,台积电发力,达到了0.6亿颗了,而三星落后了,只有0.518亿颗,英特尔则只有0.446亿颗,intel最差了。

然后是5nm,台积电最领先,而三星落后了,intel则改名为intel4,在晶体管密度上算上追上了台积电。

到3nm时,三星彻底落后了,晶体管密度只有1.5亿颗每平方毫米,只有台积电的5nm水平了,当然intel在这一块,还是不玩虚的,表现不错的,达到了2.2亿颗每平方毫米。

从上图,大家可以很明显的看出来,进入14nm之后,大家在XX纳米时的水平,其实完全是不一样的,台积电和intel可能还有拼一拼的能力,但三星确实不行了,所以三星的客户越来越少。

由此可见,接下来的芯片工艺,我们真不能用XX纳米来比较,不能认为谁小,谁就先进,真正比较的,应该是晶体管密度,你觉得呢?